About Course

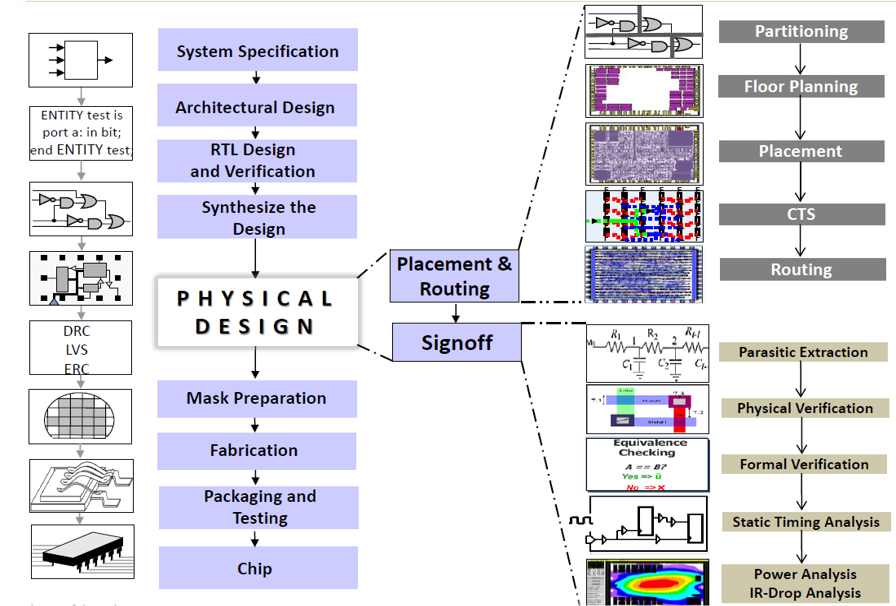

- Get complete knowledge regarding backend design and physical design flow.

- Analyze the different steps, such as floorplan, placement, cts, and routing, in the physical design flow.

- Analysis of timing analysis, congestion, and utilization in each step.

- Study of physical verification, including design rule check and layout vs schematic.

Course Content

Introduction to ASIC & Physical Design Flow

Floorplan

Power planning

Placement

Clock Tree Synthesis (CTS) & Signal Integrity

Routing

Signoff Stages: Physical Verification

Static Time Analysis (STA) and Timing Closure

Issues In PD

Engineering Change Order (ECO)

Student Ratings & Reviews

No Review Yet